El futuro de las operaciones de espectro electromagnético (EMSO) utilizadas en el ámbito militar requiere un nuevo enfoque en la arquitectura de estos sistemas. Dadas las tecnologías actuales, una arquitectura de un solo chip ofrece el mejor enfoque al integrar un front-end analógico de radiofrecuencia, lógica de matriz de puertas programable en campo tradicional, bloques IP duros de procesamiento de señales digitales (DSP) dedicados y núcleos de procesamiento vectorial para proporcionar una solución informática de un solo chip verdaderamente flexible y de bajo consumo energético, que está bien equipada para ser la piedra angular de cualquier sistema EMSO futuro.

Today’s contested and congested electromagnetic spectrum requires new solutions to meet increasingly demanding electromagnetic spectrum operations (EMSO) mission requirements. Wider bandwidth and frequency agility are increasingly necessary for these systems, placing new demands on both the radio-frequency (RF) analog front end (AFE) and the digital signal processing (DSP) portions of the system.

Traditionally, these two portions of the system have been conceived, designed, and implemented separately because the engineering skill sets are different and usually organized in distinct and separate groups. The connection between the AFE and DSP processing is usually accomplished through a JESD204 SERDES [standardized serializer/deserializer] interface. Even though the segregated design approach provides more freedom for each, it is becoming necessary to consider the analog and digital portions in a unified way.

Field-programmable gate arrays (FPGAs) provide a very efficient way to implement custom, reconfigurable, low-latency DSP algorithms; however, increasing demands of EMSO systems require massive amounts of DSP compute resources in a size, weight, and power (SWaP)-friendly form factor that is not possible with the traditional FPGA and discrete AFE approach.

Current and future EMSO systems need increased analog performance and more efficient DSP in a SWaP-optimized design, while maintaining the customization and low latency of a traditional FPGA-based solution. Industry trends show that a single-chip device architecture, which integrates a variety of compute devices into a single silicon device, is the best way to address both the demanding analog and signal processing requirements of modern EMSO systems with today’s technology.

Analog system requirements: bandwidth, latency, SWaP

Traditional EMSO system designs separate the RF AFE from the DSP system and use a JESD204 interface to move the data between the two. While this approach works for older systems, the extremely high sample rates and low latency required by modern EMSO systems break the traditional architecture. (Figure 1.)

Another solution is to use downconverters and other signal processing within the AFE to limit the amount of data sent to the downstream DSP device. Because this signal processing is built into hardware, it can be more efficient than a software or FPGA-based solution doing the same function. However, the designer is forced to make choices when developing the AFE that might not be appropriate for a given application. This approach also leaves little room to modify the behavior of this signal-processing chain. Additionally, the bandwidth limitation between the two devices means that while the overall system might have wideband performance, this is limited only to the portion of the signal-processing chain contained in the data converter.

One approach that removes these constraints is to fully integrate the RF AFE within the DSP device, creating a single-chip AFE and DSP solution that eliminates any serialization or deserialization. This move results in the lowest possible latency between the RF and the DSP system. Furthermore, there is no question of pin or bus limitations between the devices because they are integrated into the same device.

Digital system requirements: throughput, flexibility, SWaP

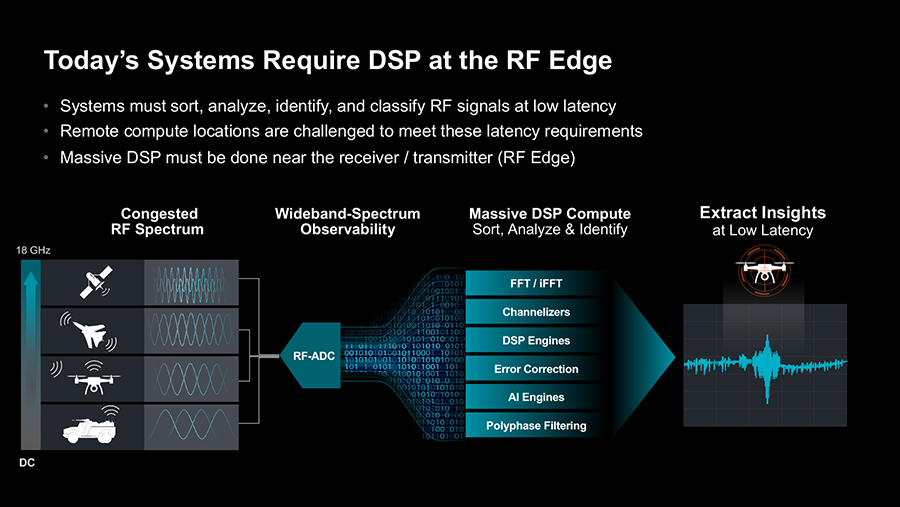

Like the RF analog portion, the DSP requirements for EMSO are also evolving and creating new challenges for system designers, such as the need to process a much wider instantaneous bandwidth (IBW). This actually increases the overall signal-processing requirements more than the linear increase in IBW, leading to the need to use larger FPGAs or multiple FPGA-based solutions to meet the DSP requirements.

One solution is to implement the signal processing in an application-specific integrated circuit (ASIC). This option would be a much more DC-power-efficient implementation than an FPGA; the downside is that ASIC development is expensive, time-consuming, and inflexible. It is also possible that during development, or even after deployment, new threats or requirements emerge. If the signal processing is based on an ASIC, the functionality is fixed, making modifications both challenging and costly.

This reality is why FPGAs are so useful to EMSO systems and are in fact widely deployed in the defense and aerospace arenas. While they don’t provide ASIC-level performance, FPGAs far exceed the performance of software solutions and are flexible enough to adapt to changing requirements, shifting workloads, and mission profiles. Caveat: While traditional FPGAs provide low latency and configurable DSP compute power, they suffer from net compute efficiency with regards to DC power. Solving the DSP demands of current and future EMSO requires very large FPGAs, or even multiples, thereby exceeding the SWaP constraints of systems.

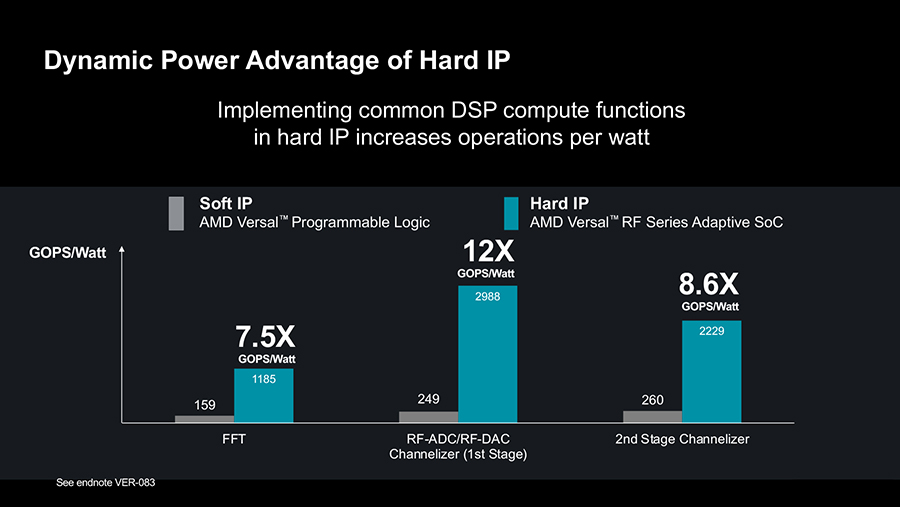

To address the massive DSP demands and SWaP requirements of EMSO systems, key DSP IP blocks can be implemented in ASIC-like hard IP blocks to reduce total power consumption and increase DSP compute. These hard IP blocks can then be integrated with an FPGA fabric to provide more DSP compute at a lower dynamic power consumption. Figure 2 shows the increase in dynamic power compute efficiency for two common DSP building blocks: FFT [fast Fourier transform] and channelizers.

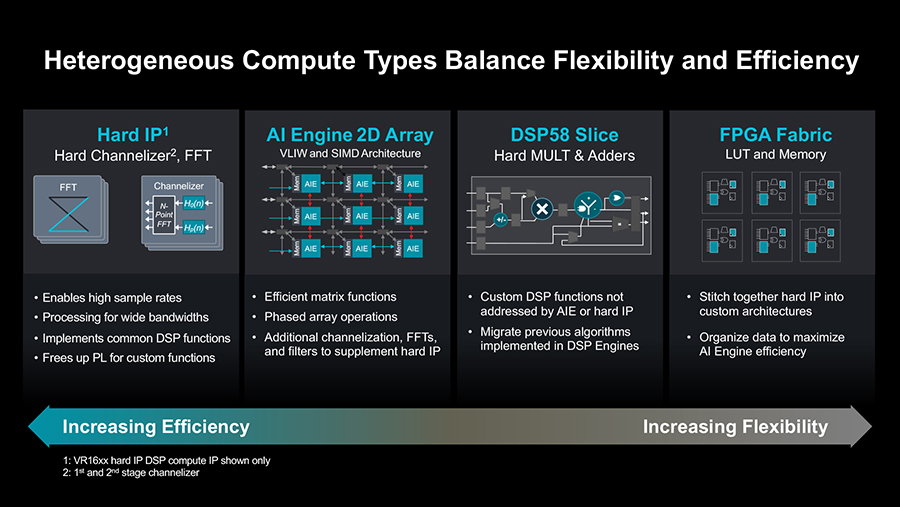

The best approach is integrating multiple compute types in a single-chip solution with the RF AFE to provide a balanced solution that can meet RF analog, DSP compute and SWaP requirements. (Figure 3.)

AMD Versal RF Series devices take a single-chip architecture approach that integrates RF AFE along with four different types of compute within a single device.

First: the traditional FPGA programmable logic of DSP slices and look-up-tables (LUTs). These provide the flexibility needed to adapt to changing requirements and mission profiles. Second is the hard IP blocks to handle the increased DSP throughput requirements. Select DSP functions implemented in dedicated hard IP blocks includes 4 GS/sec FFT/iFFT, the channelizer, polyphase arbitrary resampler, and the LDPC [low-density parity check, a class of error-correction codes] decoder. Implementing these key DSP functions in dedicated IP blocks delivers notably better power and area savings compared to soft-logic implementations and enables more compute power in the same physical area to meet constrained form-factor requirements.

Third are the AI engines for DSP, which are an array of SIMD [single instruction, multiple data] vector processors that can perform several signal-processing functions – including filters and beamforming – and can also handle neural networks. Because they include a floating-point path, they could also be used downstream of the other signal-processing blocks, adding dynamic range for these later stages. The total DSP compute power provided by the top of stack Versal RF Series devices would require multiple FPGAs for an equivalent computing solution. The amount of programmable logic required to meet processing requirements is also minimized, further reducing size and weight.

Finally, the devices include an Arm subsystem – both standard application cores as well as real-time cores – that turns them into true software-defined, adaptive system-on-chips, providing drivers for programming the integrated high-resolution RF data converters, as well as a means of controlling the rest of the digital signal processing fabric.

Bringing it all together

The future of EMSO requires a new approach to designing systems: A single-chip architecture integrating RF AFE, traditional FPGA programmable logic, dedicated DSP hard IP blocks, and vector processing cores can provide a flexible and power efficient single-chip computing solution that can serve as the backbone of a future EMSO system.

Notes

1 Based on an AMD internal analysis to calculate the theoretical DSP compute (including hard IP, AIEs, and DSPs) offered by the Versal RF VR16xx devices, and on AMD engineering projections in November 2024, using the hard IP functions in Versal RF Series devices to measure dynamic power versus the total power calculation of an AMD soft logic implementation, as measured with AMD Power Design Manager (2023.2.2), based on AMD Vivado 2023.2.2 IP catalog.

Fuente: https://militaryembedded.com